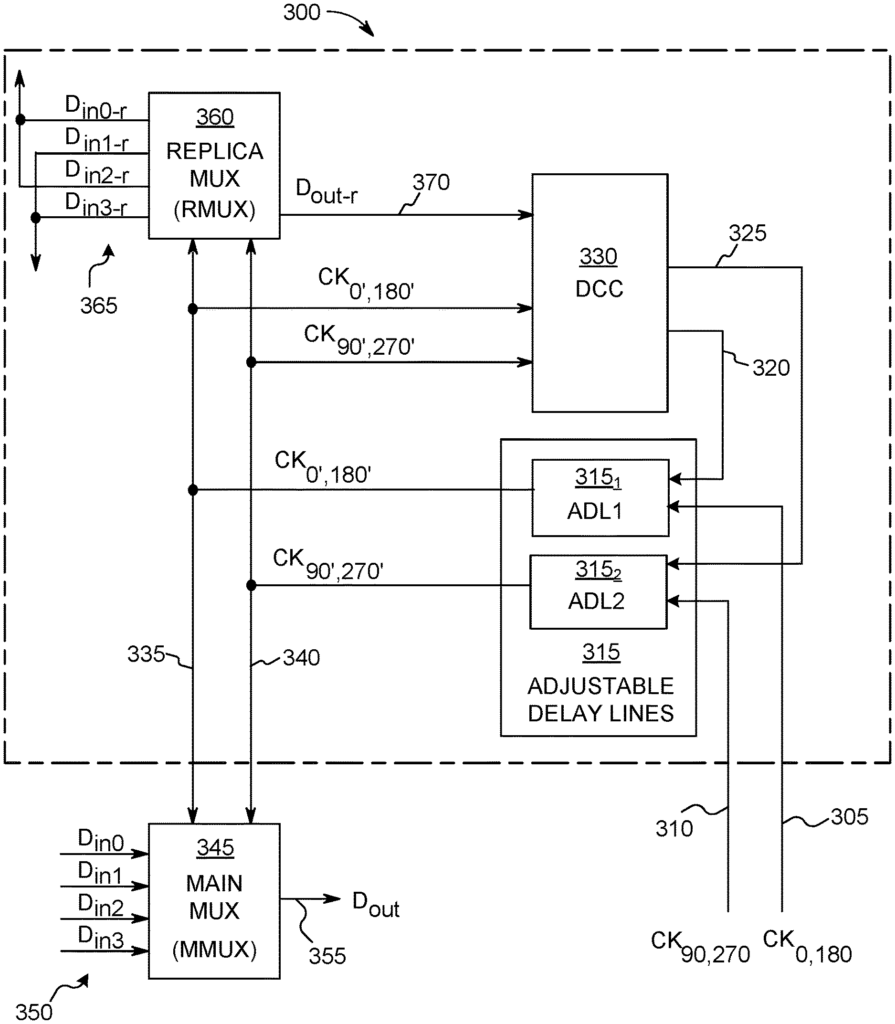

Apparatus and associated methods relate to a high-speed data serializer with a clock calibration module including a main multiplexer (MMUX), a replicated multiplexer (RMUX), a duty cycle calibration module (DCC), and a set of adjustable delay lines (ADLs), the ADLs generating calibrated clocks from a set of system clocks, the DCC sensing duty cycle and phase of the calibrated clocks. In an illustrative example, the DCC may generate error signals indicative of deviation from an expected duty cycle using low-pass filters. The error signals control the ADLs, which may provide continuous corrections to the calibrated clocks, for example. The MMUX and RMUX may receive the calibrated clocks, the RMUX generating a duty cycle indicating clock-to-data phasing, the MMUX providing live data multiplexing, for example. Various multiplexer calibration schemes may reduce jitter, which may facilitate increased data rates associated with high-speed serial data streams.